After TSMC went through its biggest cyclical correction in more than a decade during 2023, the dominating foundry surprised the markets with an extremely bullish outlook for 2024, guiding for growth rates to return to levels seen during the 2020 - 2022 semiconductor boom. The company’s CEO, CC Wei, on the earnings call:

“In 2023, weakening global macroeconomic conditions, high inflation and interest rates exacerbated the global semiconductor inventory adjustment cycle. The semiconductor industry excluding memory declined about 2%, while the foundry industry declined 13% year-over-year and TSMC's revenue declined 8.7% in U.S. dollar terms.

Our business has bottomed out and we expect 2024 to be a healthy growth year supported by continued strong ramp of our industry-leading 3-nanometer technologies, strong demand for the 5-nanometer technologies, and robust AI-related demand.

Coming off the steep inventory correction and low base of 2023, for the full year of 2024 we forecast the overall semiconductor market excluding memory to increase by more than 10% year-over-year, while foundry industry growth is forecast to be approximately 20%. For TSMC, supported by our technology leadership and broader customer base, we are confident to outperform foundry industry growth. We expect our business to grow quarter-over-quarter throughout 2024, and our full year revenue is expected to increase by low to mid-20% in U.S. dollar terms.”

TSMC’s revenue growth has been driven by moving to more advanced technologies:

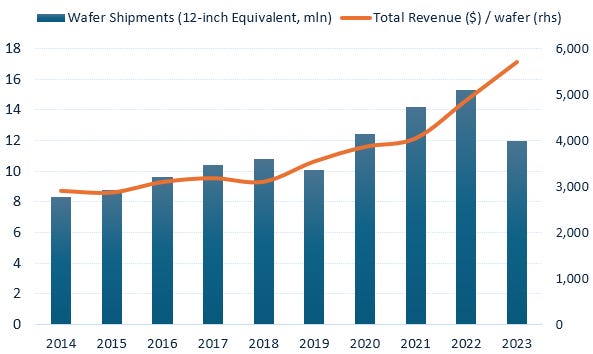

Which resulted in growing both the number of wafers shipped as well as the average selling prices:

CC Wei updated us on the status of the company’s latest N3 node, which is now ramping up:

“Our 3-nanometer technology are the most advanced semiconductor technology in both PPA and transistor technology. As a result, almost all the world’s smartphone and HPC innovators are working with TSMC. N3E further leverages the strong foundation to extend our N3 family with enhanced performance, power and yield. N3E has already entered volume production in the fourth quarter of 2023.

Supported by robust demand from customers in both smartphone and HPC applications, we expect revenue from our 3-nanometer technology to more than triple in 2024 and account for a mid-teens percentage of our total wafer revenue. We also continue to provide further enhancement of our N3 technology, including N3P and the N3X. With our strategy of continuous enhancements of our 3-nanometer process technologies, we expect strong multi-year demand from our customers and are confident that our 3-nanometer family will be another large and long-lasting node for TSMC.”

After N3, we’ll get N2 in 2025, CC Wei explains:

“We are serving a much higher level of customer engagement at N2 as compared with N3 at a similar stage from both HPC and smartphone applications. Our 2-nanometer technology will adopt narrow sheet transistor structure and be the most advanced semiconductor technology in both density and energy efficiency when it will be introduced in 2025.

Our N2 development is progressing well, with device performance and yield on track or ahead of plan. N2 is on track for volume production in 2025 with a ramp profile similar to N3. As part of our N2 technology platform, we also developed the N2 with backside power rail solution, which is better suited for specific HPC applications. N2 with backside power rail will be available in the second half of 2025 to customers, with production in 2026. This will enable TSMC to capture the AI-related growth opportunities going into the future.”

Nikkei Asia recently published a nice overview on the evolution of transistor technologies and I also published a wider deep dive on what’s next in leading edge semis here, including moving vertical.

Intel provided a nice overview recently of frontside vs backside power delivery. While this chip architecture introduces a new set of challenges, most notably in increased manufacturing complexity — which will be good for semicap names — but in return we get performance gains due to the higher transistor density and better signal integrity on the front side:

Although TSMC has been the dominant foundry with a global market share of close to 60%, there are a number of reasons why the company should expect more credible competition in the years ahead..

Firstly, TSMC took process leadership as from 2018 with its key competitor Intel falling far behind — it felt like forever that the latter was on 14 and 10nm — but under the new leadership of Pat Gelsinger, who’s been changing the incentive structures in the company, it’s looking like this former champion is becoming more competitive again. In the best case scenario for Intel, they will be able to retake process leadership, and combined with the fact that their fabs will be in geopolitically-safe countries such as the US, Ireland and Germany, this can put the company in a position to attract volumes to their new foundry business (IFS).

Additionally, Intel will be the first to introduce backside power delivery, and while TSMC claims that their N3 is still much superior, naturally Intel is claiming the reverse. Intel’s CEO discussing their Caesar-like speed in moving from node to node on the call this week:

“Our two lead vehicles in Intel 3 are on track, and we look forward to launching Sierra Forest in first half ‘24 followed shortly thereafter by Granite Rapids. Sierra Forest has final samples at customers and the production stepping of Granite Rapids is running ahead of schedule. We are even more excited about breaking into the angstrom era with Intel 20A and Intel 18A. We are first in the industry to have incorporated both gate-all-around and backside power delivery in a single process node, two years ahead of our competition. Arrow Lake, our lead Intel 20A vehicle will launch this year. Intel 18A is expected to achieve manufacturing readiness in second half ‘24, completing our 5 nodes and 4-year journey and bringing us back to process leadership. I am pleased to say that Clearwater Forest, our first Intel 18A part for servers has already gone into fab and Panther Lake for clients will be heading into fab shortly.

I’ll tell you, as we’ve been going through the development process, backside power on 18A has been elegant, beautiful, high yield, very clean in its introduction into the process. And really, the focus has been on the new transistor structure with gate all around. As customers are taking advantage of that, they’re really seeing great benefits from backside power. In some cases, almost as much performance benefit and significant area benefit from gate all around transistors.

We are confident 5 nodes in 4 years. This was audacious. It’s been superbly executed and we are on track to deliver it and get back to process technology leadership for both our products as well as to establish a major foundry opportunity for the industry rebuilding Western supply chains.”

While some of Intel’s businesses remain problematic, it is highly likely that their market share losses in datacenter CPUs will continue for example, a business that is already not profitable. The advances in their process technology however will allow the company to put up a much better fight as they defend their core CPU turf both from AMD and ARM-based silicon designed by a variety of startups, new entrants, and not least the hyperscalers themselves. And this also provides scope to gradually build up volumes in the foundry business and start competing with TSMC.

TSMC took some jabs at Intel’s 18A during the previous earnings call and confirmed these statements this time, TSMC’s chairman Dr. Mark Liu:

“I think C.C. has been very modest. I think he’s claimed that our N3P is comparable to their 18A. We still affirm our statement.”

These are the statements from the previous call Mark Liu is referring to, made by CC Wei:

“Our internal assessment shows that our N3P technology demonstrated comparable PPA to 18A, my competitor’s technology, but with an earlier time to market, better technology, maturity and much better cost. In fact, let me repeat again, our 2-nanometer technology without backside power is more advanced than both N3P and 18A and will be semiconductor industry’s most advanced technology when it is introduced in 2025.”

Secondly, Samsung has been the first to move to the next-generation of GAA transistor technology, and while I’ve seen reports that they are struggling with yield issues, there is a risk for TSMC that as Samsung resolves these they will be in a better position to attract more volumes to their foundry. Samsung also has the benefit of being located in South-Korea, which can be seen by investors and customers as to be a safer location than Taiwan.. As illustrated above, GAA has performance advantages compared to the FinFET transistor technology which TSMC is still working from.

So it is notable that TSMC’s competitors have moved quicker to both GAA and backside power delivery, and while the jury is still out on which manufacturer made the best architectural decisions, the risk certainly has increased that Samsung and Intel will become more effective competitors.

However, leading edge semiconductor design has become an extremely costly process, going into the high hundreds millions of dollars, combined with a shortage of engineering talent. So my understanding is that a company will only be able to complete a design on the process design kit (PDK) of one foundry, or at least this is what Jensen Huang, Nvidia’s CEO, alluded to last year in an interview with Nikkei Asia:

“We don’t dual-source the chips because the technology is too hard to do it twice. It’s barely possible to do one time.”

Therefore, in the near and medium term future at least, I’m not expecting large market share shifts away from TSMC.

On AI, TSMC sounded very bullish, the company’s CEO going into this topic:

“AI’s CAGR is about 50% and we are confident that we can capture more opportunities in the future. Up to 2027, we are going to have high teens of the revenue from a very narrow definition of the AI application process, not to mention the networking and all the others. All the edge devices, including smartphones and PCs, they start to put AI applications inside. They have some kind of a neuro process for example, so the silicon content will be greatly increased.”

As we noted last time, a mid single increase in the die size, which the company mentioned last time for the neural processing unit, actually gives a double digit increase in the number of wafers that need to be processed:

Staying on the AI topic, advanced CoWoS packaging was the major bottleneck within Nvidia’s supply chain last year, otherwise revenues would have even been multiples higher! TSMC was really the only CoWoS supplier last year and obviously was running at full capacity. In the meanwhile, Nvidia has also been qualifying other packaging firms to diversify their supply chain and these are in the process of building up capacity. That said, TSMC is likely to retain a high market share in this area as well, and this should stay above 50%.

TSMC’s CEO discussed the CoWoS and SOIC situation on the call:

“CoWoS demand is very strong. Today’s situation is that we cannot offer enough capacity and that condition will continue probably all the way to next year, although we are working very hard to increase capacity. For example, this year, we are doubling our output, this is still not enough, and so we will continue to increase next year.

We invested in advanced packaging technology for more than 10 years. So we expect the growth rate for CoWoS or for SOIC 3D-IC, it will be more than a 50% CAGR in the next few years at least.”

CoWoS is basically placing dies horizontally next to each other into one module, whereas SOIC is used to stack them vertically on top of each other. So with CoWoS, you can place HBM dies next to a GPU die for example as Nvidia is doing in the H100, whereas SOIC is used to place dies on top of each other, as AMD is doing in their latest MI300 GPU.

In the near term, TSMC is still seeing some smartphone seasonality headwinds during Q1, with shipments fully taking off in Q3 and Q4 of this year:

Due to the N3 ramp, the company is guiding for margin impacts this year however. TSMC’s CFO explains:

“On the plus side, we expect our utilization rate to rise in 2024 as our business recovers. However, N3 is expected to dilute our gross margin by about 3 to 4 percentage points for the full year of 2024 as the revenue contribution will be much higher than in 2023. We have a strategy so that some of our N3 capacity can be supported by N5 tools given the strong multiyear demand. Such a plan will enable higher capital efficiency in the mid to long term, but requires cost and effort in the near term. Most of this conversion will occur in second half of 2024, and we expect it to dilute our gross margin by about 1 to 2 percentage points in second half of 2024. Long term, we continue to forecast a gross margin of 53% and higher.”

So while TSMC is guiding for solid top line growth this year, the company is actually guiding for gross margins to move towards 50%:

On long term capex, TSMC sounded pretty conservative, but this wouldn’t be the first time. Also during 2018 the company was making similar sounds and then we headed into a major capex boom over the 2019 - 2023 period:

The company’s CFO detailing their capex plans:

“In 2023, we spent USD 30.4 billion, lower than our prior guidance of approximately USD 32 billion, as we continue to tighten up our capital spending where appropriate given the near-term uncertainties. In 2024, our capital budget is expected to be between USD 28 billion and USD 32 billion.

Capital intensity in the past 3 years, the highest point was 2021, it was over 50%. This year, if you do the math, is going to be mid-30s. We expect the next several years, it will remain around the 30 percentage capital intensity.

At TSMC, a higher level of capital expenditures is always correlated with higher growth opportunities in the following years. In the past few years, we have sharply increased our CapEx spending in preparation to capture or harvest the growth opportunities from HPC, AI and 5G megatrends.”

The company’s overseas investments in Japan seem to be going very smooth as an opening ceremony will be held next month for the 12-28nm fab, with press speculation that additional fabs and including advanced ones, will be constructed in the country. This is in contrast to the US, where there have been press reports that the company has been struggling with unions and in the hiring of a local engineering workforce. TSMC’s Chairman discussed the current overseas fab expansion plans:

“The second fab in Japan is in serious evaluation stage, we haven’t announced it to the public yet, and we’re still discussing with the Japan government. They are very cooperative and that technology will still be either 7 or 12-16 technologies. And remember, our Kaohsiung fab, the first fab used to be 28 and 7 nanometer, now it’s becoming 2 nanometer.

In Arizona, we are in close and constant communication with the U.S. government on incentive and tax credit support, while making strong progress in facility supply chain infrastructure, utility supply and equipment installation for our first fab. We continue to work closely and develop strong relationships with our local union and trade partners in Arizona. We are well on track for volume production of N4 process technology in the first half of ‘25 and are confident that once we begin operations, we will be able to deliver the same level of manufacturing quality and reliability in Arizona as from our fabs in Taiwan.

The second fab shell is under construction, but what technology is still under discussion, and that also has to do with how much incentives that the US government can provide. And yes, there will be a gap, the current planning is ‘27 or ‘28.

All the fabs overseas, what technology is being set up really is a decision of customers’ demand in that area. So nothing is definitive, we are trying to optimize the value of the overseas fab for TSMC.”

ASML’s record quarter

Although both TSMC and the memory makers have been making conservative noises on their capex spending for the coming years, highlighting the ability to re-use tools from previous nodes in the ramp of their next-gen nodes for example, ASML delivered a whopping quarter with record orders:

The company had been promising strong revenue growth to come in ‘25, and as currently lead times are still around 15 months, those orders had to start coming in for the company to meet that guidance.

As usual, ASML delivered, and this is no surprise as the company has extremely good visibility on the semi supply chain — the leading edge manufacturers will guide ASML in detail on the number of tools they think they’ll need as ASML needs to have the manufacturing capacity ready. ASML has a tremendously complex supply chain so the whole chain needs to be ready really, you can’t just amp up the production of EUV tools suddenly. As such, historically ASML has been providing the best guidance on how much the manufacturers are going to spend.

CEO Peter Wennink discussed the outlook for the company:

“We finished the year with a solid backlog of EUR 39 billion. The uncertainty remains in the market due to a number of global macro concerns, while the semiconductor industry is currently working through the bottom of the cycle. Industry end-market inventory levels continue to improve, moving towards more healthy levels.

Lithography utilization levels are still running lower than normal, but are now improving in both logic and memory. We expect utilization levels to continue to improve over the course of this year. While we see some positive signs of recovery, we feel it might be a bit too early to change our perhaps conservative view as communicated last quarter, and therefore still stay with our previously communicated expectation of 2024 revenue to be similar to 2023.

Customers are indicating they are seeing healthy growth this year, primarily driven by AI-related demand for both Logic and Memory but also from other end-markets as inventory levels improve. For Memory, inventories are approaching normal levels and customers are expecting to see demand growth on a number of end-markets this year. Litho demand is primarily driven by DRAM technology node transitions in support of advanced memories such as DDR5 and HBM in support of AI-related demand.”

The company did around EUR 22 billion of system sales in ‘23 (excluding services & consumables, i.e. Installed Based Management), so the current backlog basically already guarantees the ‘24 revenue guidance with growth up to H1 of 2025.

ASML also showed this nice chart on the semi cycle, highlighting the deep through the industry has been working through post the covid semi boom:

The company illustrated where their tools will be going in the coming years — clearly we should be looking at a strong investment cycle:

Also on the next-gen high-NA tool the company sounded bullish, ASML’s CEO discussing this topic:

“Everything that we’re currently seeing in terms of multi-patterning low-EUV, high-NA is very clearly the most cost-effective solution. We have double-digit orders in the order book, and we comfortably added a couple to those. Those customers give us those orders because they do those calculations and they see this.

In memory, I think high-NA will be introduced way before 3D-DRAM. So it will just be introduced in about the same time frame as logic. So it’s not a competing technology in that sense from a timing point of view. In the order intake that we see for high-NA, we equally see memory orders as we see logic orders. So I think it is clear that customers are looking at the same time frame for the introduction of high-NA, both into Logic and into Memory.”

It’s fair to say there have been mixed signals so far on high-NA demand, TSMC’s CEO for example still sounded quite dismissive on the last earnings call, this is in response to an analyst’s question why they’re not inserting high-NA in their next process technologies:

“I’m not very sure everybody knows the high-NA, but let me answer the question. We always make the right decision and our track record shows that. Is that enough? Okay. Let me elaborate a little bit more because of technology itself is of no value, only one you can serve your customer. So we always work with our customers to give them the best transistor technology and the best power-efficient technology, and at a reasonable cost, okay? And more importantly, the technology maturity that’s in the high-volume production, that’s all that’s important.”

Intel on the other hand has been a high-NA bull, this is CEO Pat Gelsinger on the recent call:

“We have begun installation of the industry’s first high-NA EUV tool in our most advanced technology development site in Oregon, aimed at addressing challenges beyond 18A.”

Another positive is that it sounded like ASML potentially has to add capacity due to strong EUV demand coming from the AI end-market, leading to increased demand for advanced Logic, HBM and DRAM wafer capacity. ASML’s CEO giving his thoughts on this topic:

“We have said our capacity buildout will be 90 EUV low-NA and 20 high-NA systems whereby internally, we are looking at that number as a base number where we’re investigating whether that number should be higher. The question is whether that 90 is going to be enough.

Now we have to realize we are selling wafer capacity, which is not only a function of the number of units, but also a function of the productivity of those tools. Now we have a pretty aggressive roadmap for the productivity in terms of wafers per hour. So it’s a complex question, but we need to look at this especially against the math that we’re seeing for litho requirements in the area of AI, whether it’s HBM or whether it is Logic, whether that is sufficient. That is a constant thing we have to look at, and that’s going to be something that I think is going to be very central when we do our Capital Markets Day by the end of the year.”

This confirms the view from SK Hynix, the leader in HBM, their CFO discussing the topic on the earnings call this week:

“The demand growth is expected at 60% per annum for the mid to long-term. And there is even some upside potential, such as the extent of AI commercialization and expansion into new applications, which if they do happen, will accelerate growth further. For HBM, the required capacity is at least twice as high to produce the same volume as conventional DRAM, which means that if there is no capacity increase, the availability of wafers for conventional DRAM would shrink significantly with HBM production ramp-up, potentially leading to very tight supply and demand for conventional DRAM, depending on the level of HBM volume expansion.”

He basically mentioned that the die size is roughly twice as large for an HBM die as it is for DRAM, and obviously larger die sizes are a positive for ASML as it means more tools will be needed to ramp up HBM production lines.

The impact from the recently announced additional US export restrictions into China should be limited, ASML communicated that they estimate the impact to be 10 to 15% of China system revenues. Basically immersion DUV systems are the tools which will now also be banned (shown below), which are still advanced technology, with multi-patterning you can get to around 5 to 7nm. The exception is the 1980 tool, which can still be sold to certain Chinese fabs, but not too others. On the latter point, it’s far from clear how the US administration is going to control the secondary market in China and make sure that these tools aren’t relocated to restricted fabs.

Coming to the financial outlook, ASML did guide for some margin headwinds during ‘24 as they ramp capacity, especially for the new high-NA tool. On the positive, the targets for a significant lift in gross margin by ‘25 are still intact. ASML’s CFO explaining these movements:

“We are still targeting our earlier communicated gross margin ambition of 54% to 56% by 2025. This increase in gross margin will be driven by a number of items. First, higher sales volume, both in EUV and DUV. Second, a move to a higher-margin EUV 0.33 NA system. Third, we expect reduced headwinds from capacity investments as we ramp volume, including for high-NA. Fourth, we will also be transitioning to a higher-margin EUV high-NA system, the 5200 in 2025.”

Financials — TSMC share price $117, ASML share price EUR 797 at time of writing

TMSC is currently reasonably attractively priced at a 2024 FCF yield of 3.6% with a PE of 19x and without dilutive SBC compensation. This for a company which has been generating 15% top line growth per annum and 18% EPS growth annually over the last five years.

TSMC’s PE multiple is currently towards the average of its long term history. A lot of the semi space has been re-rating, so TSMC is definitely looking attractively priced compared to its peers.

Historically, my rule of thumb has been as long as there is a strong path for Moore’s law to continue, to stay long ASML. However, I do take profits when valuations or the cycle are looking stretched. In the case of ASML, we’re looking again at a peak multiple with the company now heading into a transition year. That said, the company is sounding very bullish on ‘25 so a lot of investors will start working based from those numbers.

Although also on ‘25 numbers, this is a pricey stock, but in return you get a company with a track record of generating a 20% top line growth rate over the last five years combined with a 27% EPS CAGR. So this is why the market is currently willing to pay 29x 2025 EPS:

My updated long-term model based on the company’s 2030 guidance and current share price, resulting in IRRs of 5 to 18%:

Historically ASML’s long term guidance has been spot on, so long term investors can still make good returns in these shares despite valuations which are now looking in the near term somewhat stretched.

If you enjoy research like this, hit the like button and subscribe. Also, please share a link to this post on social media or with colleagues with a positive comment, it will help the publication to grow. All shares are appreciated.

I’m also regularly discussing tech and investments on my Twitter.

Disclaimer - This article is not a recommendation to buy or sell the mentioned securities, it is purely for informational purposes. While I’ve aimed to use accurate and reliable information in writing this, it can not be guaranteed that all information used is of this nature. The views expressed in this article may change over time without giving notice. The future performance of the mentioned securities remains uncertain, with both upside as well as downside scenarios possible.

That was a great write-up, thank you! 🙏

Amazing job man, ASML is my second biggest position and reading people like you that understood the business and the growth opportunities always feels good!